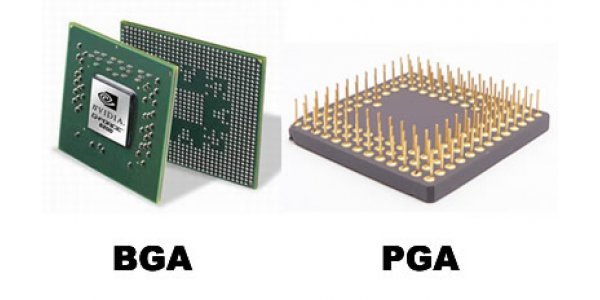

1. BGA Package

On the back side of the printed circuit board, a spherical bump is produced in a display manner to replace the pins. An LSI chip is assembled on the front side of the printed circuit board, and then sealed by molding resin or potting. The pin can exceed 200, which is a package for multi-pin LSI. The package body can also be made smaller than QFP (Four-Lead Flat Package). For example, a 360-pin BGA with a lead center distance of 1.5mm is only 31mm square; a 304-pin QFP with a lead center distance of 0.5mm is 40mm square. And BGA does not have to worry about pin deformation problems like QFP.

The BGA package's I / O terminals are distributed under the package in a circular or columnar solder joint in an array. The advantage of BGA technology is that although the number of I / O pins has increased, the pin pitch has not decreased but increased, thereby improve assembly yield; although its power consumption has increased, BGA can be soldered using a controlled collapsed chip method, which can improve its electrical and thermal performance; thickness and weight are reduced compared to previous packaging technologies; parasitic parameters are reduced, the signal transmission delay is small, and the frequency of use is greatly increased; assembly can be coplanar welding, high reliability.

TinyBGA (Tiny Ball Grid Array), a small ball grid array package, belongs to a branch of BGA packaging technology. The ratio of the chip area to the package area is not less than 1: 1.14, which can increase the memory capacity by 2 to 3 times without changing the volume of the memory. Compared with TSOP package products, it has a smaller size and better heat dissipation.

Memory products using TinyBGA packaging technology have only 1/3 the volume of a TSOP package with the same capacity. The pins of the TSOP packaged memory are led out around the chip, while TinyBGA is led out from the center of the chip. This method effectively shortens the signal transmission distance, and the length of the signal transmission line is only 1/4 of the traditional TSOP technology, so the signal attenuation is also reduced. This not only greatly improves the anti-interference and anti-noise performance of the chip, but also improves the electrical performance. Using TinyBGA package chip can resist FSB up to 300MHz, while using traditional TSOP packaging technology can only resist FSB up to 150MHz.

The memory of TinyBGA package is also thinner (package height is less than 0.8mm), and the effective heat dissipation path from the metal substrate to the heat sink is only 0.36mm. Therefore, TinyBGA memory has higher heat conduction efficiency, which is very suitable for long-running systems and has excellent stability.

Advantage:

1.1 The memory packaged with BGA technology can increase the memory capacity by two to three times without changing the volume.

1.2 Memory products using BGA packaging technology are only one-third the size of TSOP packages at the same capacity.

1.3 Compared with the traditional TSOP packaging method, the BGA packaging method has a faster and effective heat dissipation path.

The opening of the stencil of the BGA package needs to be reasonably adjusted according to the size and clearance of the BGA chip pin sphere. The reasonable value must be adjusted between the virtual soldering and the short circuit. It must refer to the chip situation and cannot be handled according to the general situation (recommended opening ratio 88% -95% ).

2. Other chip packaging technologies

2.1 C- (Ceramic) It is a symbol for ceramic package. For example, CDIP stands for ceramic DIP.2.2 COB (Chip on board) is one of the bare chip mounting technologies. The semiconductor chip is handed over and mounted on a printed circuit board. The electrical connection between the chip and the substrate is achieved by wire stitching and covered with resin to ensure reliability. Although COB is the simplest bare chip placement technology, its packaging density is far inferior to TAB and flip-chip bonding technologies.

2.3 DIP (Dual in-line package)

Double in-line package, one of the plug-in packages, the pins are drawn from both sides of the package, and the package materials are plastic and ceramic. European semiconductor manufacturers often use DIP.

DIP is the most popular plug-in package, and its applications include standard logic ICs, memory LSIs, and microcomputer circuits. The pin center distance is 2.54mm, and the number of pins is from 6 to 64. Package width is usually 15.2mm. Some packages with a width of 7.52mm and 10.16mm are called SK-DIP (Skinny Dual in-line package) and SL-DIP (Slim Dual in-line package) narrow body DIP, respectively. However, in most cases, no distinction is made, and they are simply collectively referred to as DIP. In addition, ceramic DIP sealed with low melting glass is also called Cerdip.

2.3.1 DIC (Dual in-line ceramic package) Another name for DIP (including glass seal) of ceramic package.

2.3.2 Cerdip: Ceramic double in-line package sealed with glass for ECL RAM, DSP (Digital Signal Processor) and other circuits. Cerdip with glass window is used for ultraviolet erasing EPROM and microcomputer circuit with EPROM inside. The lead center distance is 2.54mm, and the number of pins is from 8 to 42. In Japan, this package is referred to as DIP-G (G means glass seal).

2.3.3 SDIP (Shrink dual in-line package). One of the plug-in packages, the shape is the same as DIP, but the pin center distance (1.778mm) is less than DIP (2.54mm), so it is called this. The number of pins is from 14 to 90. There are ceramic and plastic. Also known as SH-DIP (Shrink dual in-line package)

2.4. Flip-chip

As one of the bare chip packaging technologies, metal bumps are prepared in the electrode area of the LSI chip, and then the metal bumps are pressure-bonded to the electrode area on the printed substrate. The footprint of the package is basically the same as the chip size. It is the smallest and thinnest of all packaging technologies. However, if the thermal expansion coefficient of the substrate is different from that of the LSI chip, a reaction occurs at the joint, which affects the reliability of the connection. Therefore, the LSI chip must be reinforced with resin, and a substrate material having substantially the same thermal expansion coefficient is used.

2.5. FP (Flat package)

One of the surface mount packages. Another name for QFP or SOP. Some semiconductor manufacturers use this name.

2.6. H- (with Heat sink)

Indicates a mark with a heat sink. For example, HSOP means SOP with heat sink.

2.7. MCM (Multi-chip module)

A package in which a plurality of semiconductor bare chips are assembled on a wiring substrate. According to the substrate material, it can be divided into three categories: MCM-L, MCM-C and MCM-D. MCM-L is a module using a common glass epoxy multilayer printed circuit board. The wiring density is not very high and the cost is low. MCM-C is a component that uses multilayer technology to form multilayer wiring and uses ceramic (alumina or glass ceramic) as the substrate, similar to a thick-film hybrid IC using a multilayer ceramic substrate. There is no significant difference between the two. The wiring density is higher than MCM-L. MCM-D is a component that uses thin-film technology to form multilayer wiring and uses ceramic (alumina or aluminum nitride) or Si, Al as the substrate. The cabling plot is the highest of the three components, but the cost is also high.